Regarding TSMC's roadmap, we have already shared a lot before. For example, not long ago, we shared TSMC's latest manufacturing roadmap, which can be referred to in the article "TSMC, the Latest Roadmap". But this is actually just the tip of the iceberg of this wafer leader's rich treasure trove.

According to a report by tomshardware, at this year's IEDM conference, TSMC suddenly shared a chip packaging roadmap containing 100 billion transistors. According to TSMC, these huge monsters will come from the collection of 3D packaging cores on a single chip package. At the same time, as shown in the figure, TSMC is also committed to developing chips that contain 200 billion transistors on a single piece of silicon.

To achieve this goal, the company reiterated its commitment to the 2-nanometer N2 and N2P production nodes and the 1.4-nanometer A14 and 1-nanometer A10 manufacturing processes, which are expected to be completed by 2030. In addition, TSMC expects packaging technologies (CoWoS, InFO, SoIC, etc.) to make progress, enabling it to build large-scale multi-Chiplet solutions with packaging of more than 100 billion transistors around 2030.

Behind this is the inevitable choice of changing the chip design paradigm.

Advertisement

Single-chip integration, the end of the strong bow

Since Gordon Moore defined "Moore's Law," the chip industry has continued to develop under the guidance of this industry's golden rule. In the decades following the invention of integrated circuits, the number of transistors integrated on most chips has increased exponentially, and the performance of the chips has also risen accordingly.

However, in recent years, due to the physical properties of the materials themselves, the bottlenecks of manufacturing equipment and processes, and architecture, it has become increasingly difficult to integrate more transistors on a single chip as in the past. However, driven by the demand for artificial intelligence and autonomous driving, the market has a very high demand for high-performance chips. This makes the continuous increase in chip performance an inevitable path. The single-chip integration scheme that has been used in the past still has a great attraction, and Nvidia and Cerebras are among the most loyal defenders. First, let's look at Nvidia, which has launched the GH100 with 80 billion transistors, which is one of the most complex single-chip processors on the market. Then let's look at Cerebras, a startup that has achieved the integration of 2.5 trillion transistors on a whole wafer.

The reason why everyone is so "nostalgic" is closely related to the characteristics of single-chip integration itself.It is understood that this is mainly related to the fact that monolithic integration involves creating an entire integrated circuit on a single semiconductor substrate, with all components (such as CPU cores, memory, and I/O interfaces) being manufactured together in a single process. Benefiting from such a design, due to the close proximity of the components, monolithic designs can usually provide excellent performance; at the same time, this proximity also reduces signal latency and power consumption, making monolithic chips an ideal choice for high-performance computing; in addition, monolithic integration can reduce the size of the chip and reduce power consumption; moreover, the on-chip communication speed in monolithic designs is faster because the components are physically closer, thus achieving lower latency and better overall system performance.

Therefore, this compact design can accumulate tens or hundreds of billions of calculations. According to TSMC, we will soon have more complex monolithic chips with more than 100 billion transistors. However, building such large processors is becoming increasingly complex and expensive. At the same time, as the chip size becomes larger, the wafer yield issue becomes more prominent.

In view of this, many companies have chosen chiplet (core) design (such as AMD's Instinct MI300X and Intel's Ponte Vecchio, which are composed of dozens of corelets), which is related to the many advantages of this design. First, corelets can easily achieve scalability and customization of integrated circuits. Manufacturers can mix and match corelets to create products with different functions, allowing them to adapt to different applications; second, the modular nature of corelets allows for parallel development, which shortens the time to market for new products. Companies can develop each corelet simultaneously, thus accelerating innovation; moreover, manufacturing smaller corelets is more cost-effective than producing large monolithic designs, especially for advanced nodes with potentially lower yields; finally, smaller chips have a higher yield because a single defective corelet does not cause the entire product to be unusable; in addition, corelets can also provide enhanced performance by optimizing processing elements for the required tasks.

While chiplet design is becoming more popular, it also puts forward more demands for packaging, because only better packaging and interconnection can better integrate these corelets, which is the reason why TSMC and its customers must develop logic technology and packaging technology synchronously. The former provides density improvement for the latter, which is also the reason why TSMC includes the evolution of production nodes and packaging technology in the same slide.

Advanced packaging, new battlefield

Previously, the semiconductor industry has reported that the United States will invest $3 billion in the development of advanced packaging, which is enough to prove the importance of packaging that was not previously favored (refer to the article "The United States invests $3 billion to vigorously develop advanced packaging"). Based on this, chip manufacturers can also package different types of components together in a more effective way, instead of using the most advanced process to manufacture each part of the chip. This can improve performance while reducing costs.

Take TSMC as an example, they have already invested heavily in packaging technology. In July of this year, TSMC stated that due to the shortage of advanced packaging capacity, the company plans to invest nearly NT$90 billion (about RMB 20.6 billion) to establish a wafer factory for producing advanced packaging in the Tongluo Science Park under the jurisdiction of Zhuke.

TSMC also stated that the company's goal is to double its advanced packaging capacity called CoWoS by 2024, which represents the company's chips on the wafer on the substrate, specifically bundling logic and storage chips together and improving the data transfer speed between them. In addition, TSMC also has multi-package technology, which is now called the 3D Fabric platform of the company. In the previous article "TSMC's Advanced Packaging" of the semiconductor industry observation, we can see the specific performance of this wafer factory in packaging.

In addition to TSMC, wafer foundry competitors Intel and Samsung are also "competing" in advanced packaging.

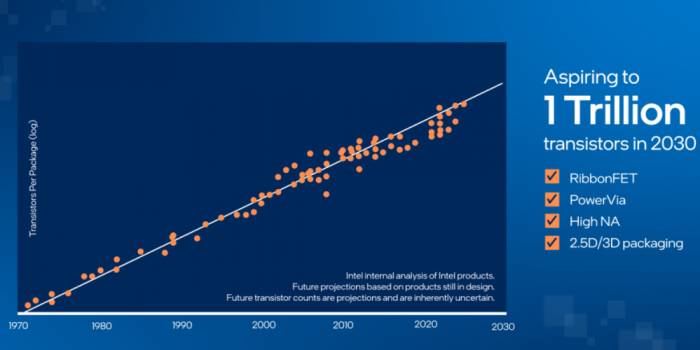

First, let's look at Intel. As a semiconductor giant that has been holding chip manufacturing technology for many years, Intel has rich experience in single-chip integration. It is no exception in the packaging field. It is worth mentioning that at last year's IEDM, Intel took the lead in proposing the ambition to build a processor with 1 trillion transistors by 2030.According to Intel, the reason for achieving such a feat is that the researchers in the company's component research group have discovered new materials and processes that blur the boundaries between packaging and silicon. Intel also revealed the key follow-up steps to extend Moore's Law to packaging with trillions of transistors, including advanced packaging that can achieve an additional 10 times the interconnect density, thus achieving a quasi-monolithic chip. Intel also pointed out that the company's material innovation has identified practical design choices, using new materials that are only 3 atoms thick to meet the requirements for transistor miniaturization, enabling the company to continue to surpass the scale of RibbonFET.

Let's take a closer look at Intel's advanced packaging. According to Intel's official website, the company has packaging technologies such as FCBGA/LGA, EMIB, Foveros, and Co-EMIB. Among them, EMIB and Foveros are the mainstays of Intel's advanced packaging. For more details, refer to the article "The Packaging Power of Intel You May Not Know."

As for Samsung, it has also made a lot of investment in packaging.

Samsung introduced that in addition to having 2.5D packaging technology I-Cube and H-Cube, the company also has 3D IC technology X-Cube. Among them, I-Cube deploys parallel horizontal chip placement to improve performance while preventing heat accumulation. Samsung's Through-Silicon Vias (TSV) and Back-End-Of-Line (BEOL) technology lay the foundation for two or more chips to coordinate their specialized functions, surpassing the sum of the parts, providing a powerful solution for modern devices. Depending on the insert type, I-Cube can be used for I-CubeS and I-CubeE derivatives.

3D IC packaging, on the other hand, further improves performance by stacking components vertically, using shorter interconnect lengths, thus achieving ultra-high vertical interconnect density and lower parasitic effects, while saving a lot of on-chip space. Samsung said that the 3D IC X-Cube technology significantly reduces the yield risk of large monolithic chips through 3D integration, enabling high system performance at a lower cost while maintaining high bandwidth and low power consumption.

In addition to these manufacturers, ASE, Amkor, and Jiangsu Changjiang Electronics are also important players in the advanced packaging market that cannot be ignored.Trillions of Transistors: TSMC's Approach

From the report above, it can be seen that advanced packaging is an inevitable support for TSMC to reach the goal of trillions of transistors. From the figure above, it can be observed that, in addition to this, TSMC will also rely on new channel materials, EUV, Metal Oxide ESL, Self-Aligned Line with Flexible Space, and Low Damage/Hardening Low-k & Novel Cu Fill, among other technologies, to achieve the goal of trillions.

Below, let's dissect some of TSMC's "secrets."

First, looking at the communication material aspect, according to TSMC, before the 7nm node, silicon has always been the preferred channel material for all CMOS technologies. However, in the era of 5nm technology, TSMC first adopted SiGe as an advanced logic production technology for p-type FinFET channel materials. Now, TSMC's transistor research team is also exploring devices based on materials with essentially 2D or 1D carrier transport (low-dimensional transport), including transition metal dichalcogenides, graphene nanoribbons, and carbon nanotubes, which are being studied and tested within TSMC.

In the past two IEDMs, we saw TSMC's researchers demonstrate MoS2 with a thickness of only one atom. The team integrated the hafnium-based dielectric formed by atomic layer deposition with the single-layer TMD material MoS2, constructing a top-gate nFET with a physical dielectric thickness of 3.4 nm and an equivalent oxide thickness (EOT) of about 1 nm.

As for EUV, it may be the design of High NA EUV or the future-oriented Hyper NA EUV. We will not discuss it here, and details can be referred to the previous article "Next-Generation EUV Lithography Machine" in the semiconductor industry observation.

TSMC also mentioned Metal Oxide ESL, Self-Aligned Line with Flexible Space, and Low Damage/Hardening Low-k & Novel Cu Fill in the roadmap. We have a basic understanding of the above technologies, but we have not seen relevant materials from related searches.

What can be affirmed is that the trillion-transistor chip is waiting for us ahead, and all of this is worth looking forward to.

Post a comment